- descrizione verbale

- automa della macchina sequenziale

- automa della rete (codifiche binarie)

- tavola degli stati futuri

- espressioni booleane delle funzioni di eccitazione e uscite

- disegno della rete

N.B.: Occorre un passo di minimizzazione dell’automa a stati finiti.

N.B.: Le espressioni booleane minimali servono per la realizzazione con porte logiche o programmable logic array (PLA), invece se si usa la read only memory (ROM) o i multiplexer (MUX) non serve eplicitare le espressioni booleane.

esempio

1. descrizione verbale

Circuito che riceve in ingresso x e produce in uscita 1 se riconosce 1101 con sovrapposizioni.

2. stati dell’automa

Sin: stato iniziale

S1: riconoscimento del primo bit

S11: riconosciuto due bit

| 0 | 1 |

|---|

| Sin | Sin/0 | S1/0 |

| S1 | Sin/0 | S11/0 |

| S11 | S110/0 | S11/0 |

| S110 | Sin/0 | S1/1 |

| Quest’automa è minimo, cioè è costruito con meno stati possibili? Si, perché non ci sono [[criterio di minimalità | stati equivalenti]]. | |

3. codifica degli stati

- Input: gli input sono già codificati.

- Stati: In tutto ci sono 4 stati, quindi ci servono 2 bit.

| y1 | y0 |

|---|

| S0 | 0 | 0 |

| S1 | 0 | 1 |

| S11 | 1 | 0 |

| S110 | 1 | 1 |

| Scritto ciò, la tabella degli stati dell’automa al passaggio 1 può essere riscritta come: | | |

| 0 | 1 |

|---|

| 00 | 00/0 | 01/0 |

| 01 | 00/0 | 10/0 |

| 10 | 11/0 | 10/0 |

| 11 | 00/0 | 01/1 |

- Output: gli output sono già codificati.

4. tavola degli stati futuri

| x (input) | y1 | y0 | | Y1 | Y0 | | z (output) |

|---|

| 0 | 0 | 0 | | 0 | 0 | | 0 |

| 0 | 0 | 1 | | 0 | 0 | | 0 |

| 0 | 1 | 0 | | 1 | 1 | | 0 |

| 0 | 1 | 1 | | 0 | 0 | | 0 |

| 1 | 0 | 0 | | 0 | 1 | | 0 |

| 1 | 0 | 1 | | 1 | 0 | | 0 |

| 1 | 1 | 0 | | 1 | 0 | | 0 |

| 1 | 1 | 1 | | 0 | 1 | | 1 |

realizzazione con i flip-flop JK

| x | y1 | y0 | | Y1 | Y0 | | z | | j1,k1 | j0,k0 |

|---|

| 0 | 0 | 0 | | 0 | 0 | | 0 | | 0 δ | 0 δ |

| 0 | 0 | 1 | | 0 | 0 | | 0 | | 0 δ | δ 1 |

| 0 | 1 | 0 | | 1 | 1 | | 0 | | δ 0 | 1 δ |

| 0 | 1 | 1 | | 0 | 0 | | 0 | | δ 1 | δ 1 |

| 1 | 0 | 0 | | 0 | 1 | | 0 | | 0 δ | 1 δ |

| 1 | 0 | 1 | | 1 | 0 | | 0 | | 1 δ | δ 1 |

| 1 | 1 | 0 | | 1 | 0 | | 0 | | δ 0 | 0 δ |

| 1 | 1 | 1 | | 0 | 1 | | 1 | | δ 1 | δ 0 |

5JK. espressioni booleane

- z è di immediato riconoscimento: z=xy1y0

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | 0 | 0 | δ | δ |

| 1 | 0 | 1 | δ | δ |

| j1=xy0 | | | | |

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | δ | δ | 1 | 0 |

| 1 | δ | δ | 1 | 0 |

| k1=y0 | | | | |

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | 0 | δ | δ | 1 |

| 1 | 1 | δ | δ | 0 |

| j0=xy1+xy1=x⊕y1 | | | | |

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | δ | 1 | 1 | δ |

| 1 | δ | 1 | 0 | δ |

| k0=x+y1 | | | | |

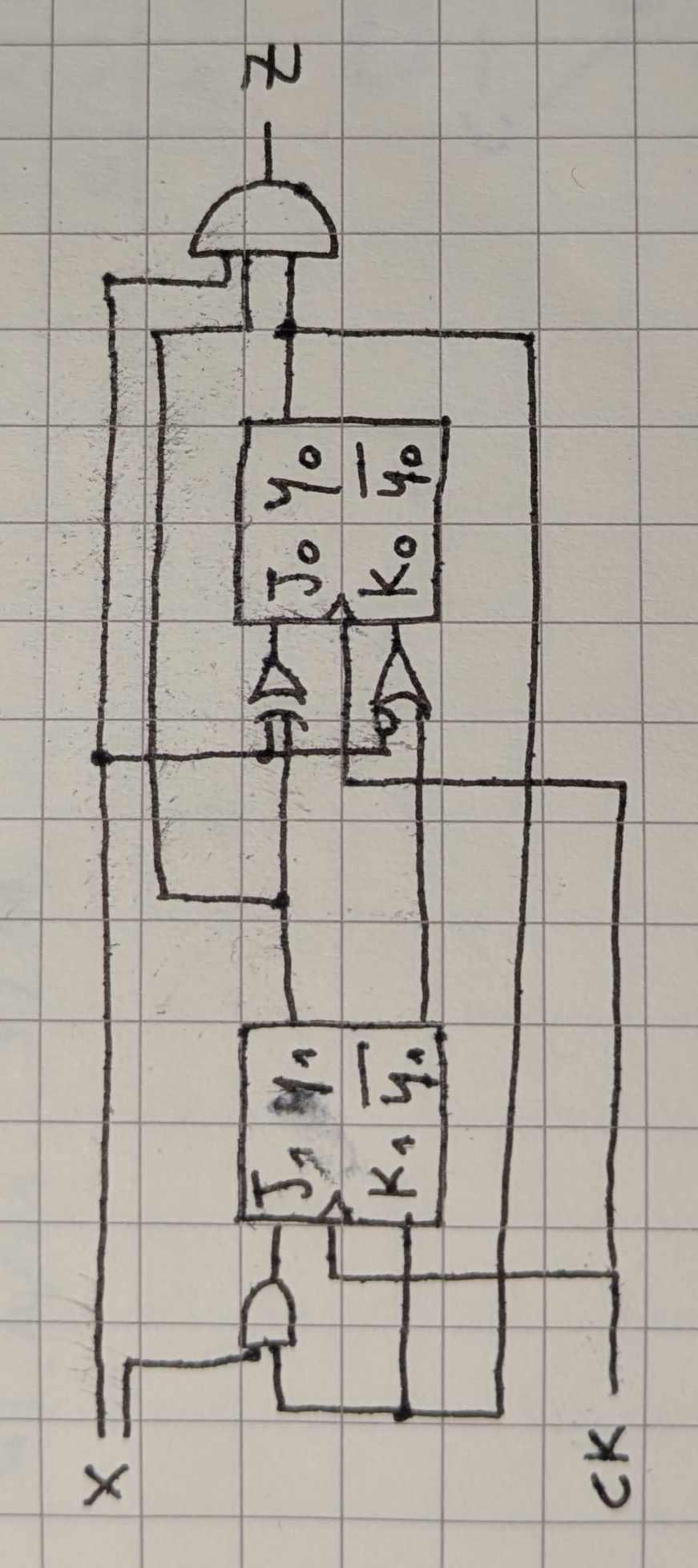

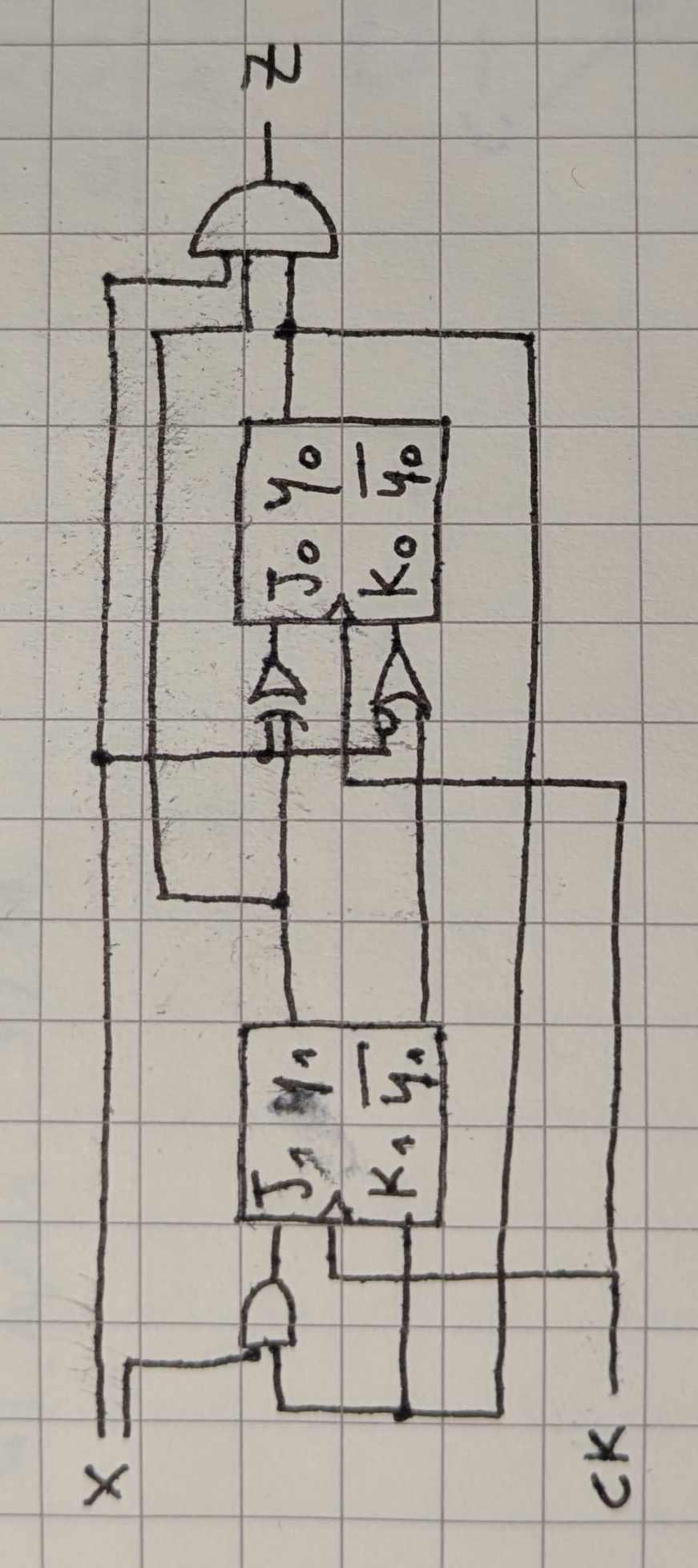

6JK. disegno della rete

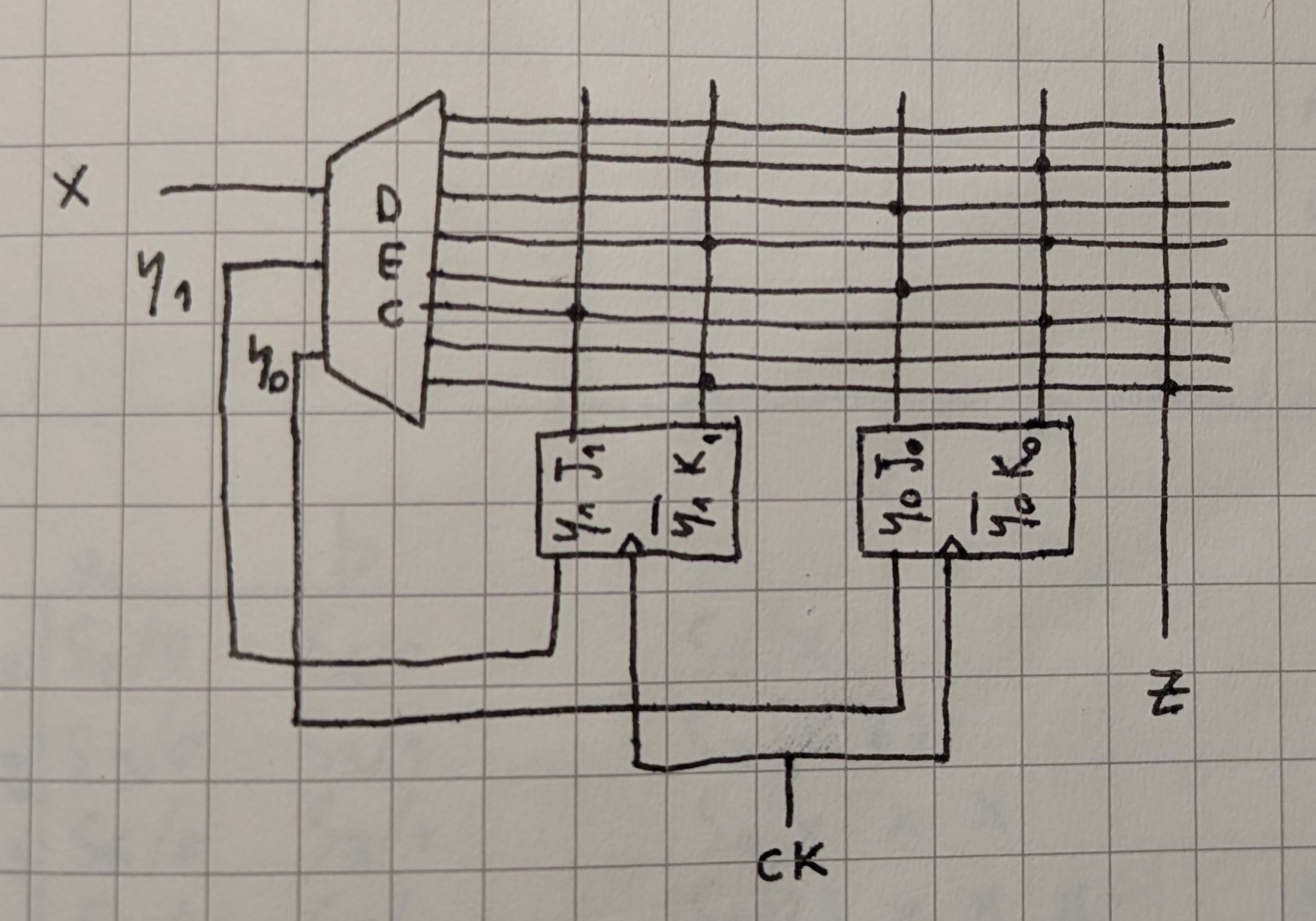

realizzazione con i flip-flop D

Ora realizziamo la stessa rete ma con i flip flop D (più semplice)

4D. tavola degli stati futuri

| x | y1 | y0 | | Y1 | Y0 | | z | | d1,d0 |

|---|

| 0 | 0 | 0 | | 0 | 0 | | 0 | | 0 0 |

| 0 | 0 | 1 | | 0 | 0 | | 0 | | 0 0 |

| 0 | 1 | 0 | | 1 | 1 | | 0 | | 1 1 |

| 0 | 1 | 1 | | 0 | 0 | | 0 | | 0 0 |

| 1 | 0 | 0 | | 0 | 1 | | 0 | | 0 1 |

| 1 | 0 | 1 | | 1 | 0 | | 0 | | 1 0 |

| 1 | 1 | 0 | | 1 | 0 | | 0 | | 1 0 |

| 1 | 1 | 1 | | 0 | 1 | | 1 | | 0 1 |

5D. espressioni booleane

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| x \ y1y0 | 00 | 01 | 11 | 10 |

|---|

| 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

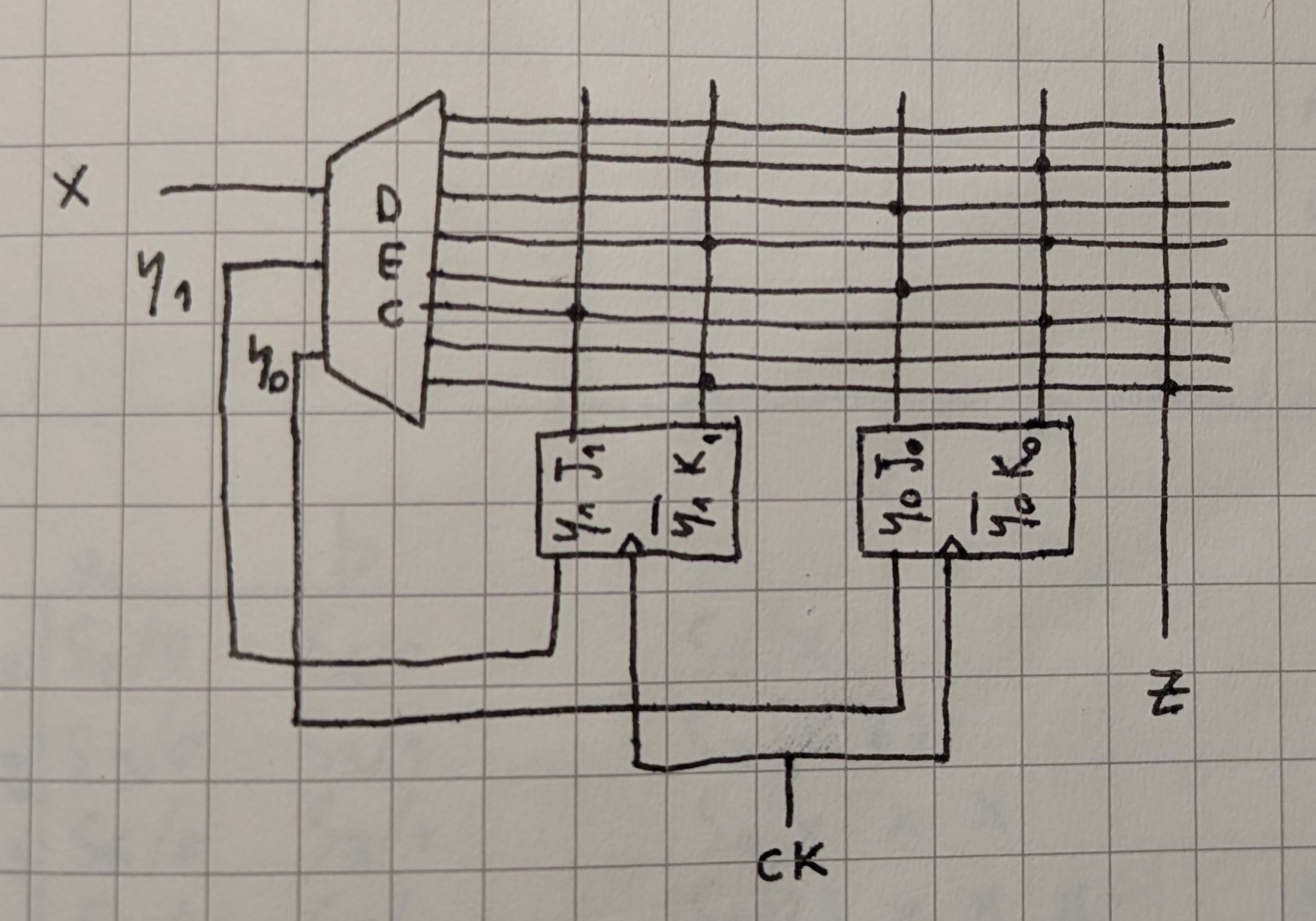

realizzazione con i flip-flop JK combinati alla ROM

N.B.: Il vantaggio è che non vanno ricavate le espressioni booleane perché i valori degli output possono essere codificati direttamente nella ROM.